| T | ab | #9   |

|---|----|------|

| _ | aυ | 11 / |

Name: \_\_\_\_\_\_ Per: \_\_\_\_\_

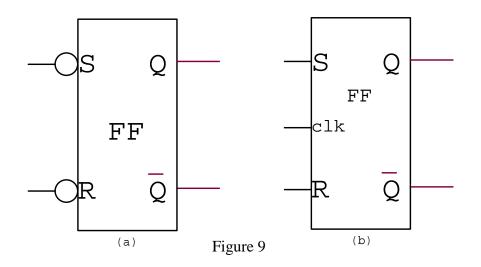

## Title: R-S FLIP FLOPS

## **Materials:**

[1] 7400 2-input NAND gate IC

[1] clock (single pulses)

## **Procedure**:

- 1. On a separate sheet of paper, **draw** a logic diagram for the R-S flip-flop shown in Fig. 9(a). Use two 2-input NAND gates.

- 2. Insert the 7400 into the breadboard.

- 3. Construct the circuit you drew in step 1.

- 4. Operate the input switches as shown in Table 9-1. Observe and record the results in the output columns. **Get Instructor's Signature.**

- 5. Have Instructor check your pulse clock if you're not sure that it works.

- 6. In the rightmost column of Table 9-1 write the name of the condition of the outputs. Use term "hold", "set", or "reset".

- 7. On a separate sheet of paper, **draw** a logic diagram for the clocked R-S flip flop shown in Fig. 9(b). Use four 2-input NAND gates.

- 8. Construct the circuit you drew in step 6.

- 9. Operate the input switches as shown in Table 9-2 and record the output results. **Get Instructor's Signature.**

## Questions: (answer on a separate piece of paper – "Draw" means you must use a template):

- 1. Describe the input conditions on the *R-S flip-flop* for the set, reset, and hold conditions. Label the inputs R & S and the outputs Q and  $\overline{Q}$ .

- 2. Describe the input conditions on the *clocked R-S flip-flop* for the set, reset, and hold conditions. Label the inputs R & S and the outputs Q and  $\overline{Q}$ .

- 3. Describe the input conditions on the *R-S flip-flop* that are considered the prohibited state/condition.

- 4. Describe the input conditions on the *clocked R-S flip-flop* that are considered the prohibited state/condition.

| Inputs |   | Outputs |                |                     |  |

|--------|---|---------|----------------|---------------------|--|

| S      | R | Q       | $\overline{Q}$ | Name of Condition   |  |

| 0      | 0 |         |                | Prohibited          |  |

| 0      | 1 |         |                |                     |  |

| 1      | 0 |         |                |                     |  |

| 1      | 1 |         |                |                     |  |

|        |   |         |                | hold, set, or reset |  |

Table 9-1 R-S Flip-Flop

| Inputs     |      |   | Outputs            |                |                   |                |                   |

|------------|------|---|--------------------|----------------|-------------------|----------------|-------------------|

| Clock      | Data |   | Before clock pulse |                | After clock pulse |                | Name of Condition |

| Clk        | S    | R | Q                  | $\overline{Q}$ | Q                 | $\overline{Q}$ |                   |

| $\uparrow$ | 0    | 0 | 0                  | 1              |                   |                |                   |

| $\uparrow$ | 0    | 1 | 0                  | 1              |                   |                |                   |

| $\uparrow$ | 1    | 0 | 0                  | 1              |                   |                |                   |

| $\uparrow$ | 1    | 1 | 0                  | 1              |                   |                | Prohibited        |

| $\uparrow$ | 0    | 0 | 1                  | 0              |                   |                |                   |

| $\uparrow$ | 0    | 1 | 1                  | 0              |                   |                |                   |

| $\uparrow$ | 1    | 0 | 1                  | 0              |                   |                |                   |

| $\uparrow$ | 1    | 1 | 1                  | 0              |                   |                | Prohibited        |

|            | •    | • |                    | •              |                   |                | hold, reset, or   |

|            |      |   |                    |                |                   |                | set               |

Table 9-2 Clocked R-S Flip-Flop